- 您现在的位置:买卖IC网 > Sheet目录1903 > AT89C51SND1C-7HTUL (Atmel)IC MCU 64KB FLASH MEM 81-CBGA

28

4109LS–8051–02/08

AT8xC51SND1C

7.3.3.2

Timings

Test conditions: capacitive load on all pins= 50 pF.

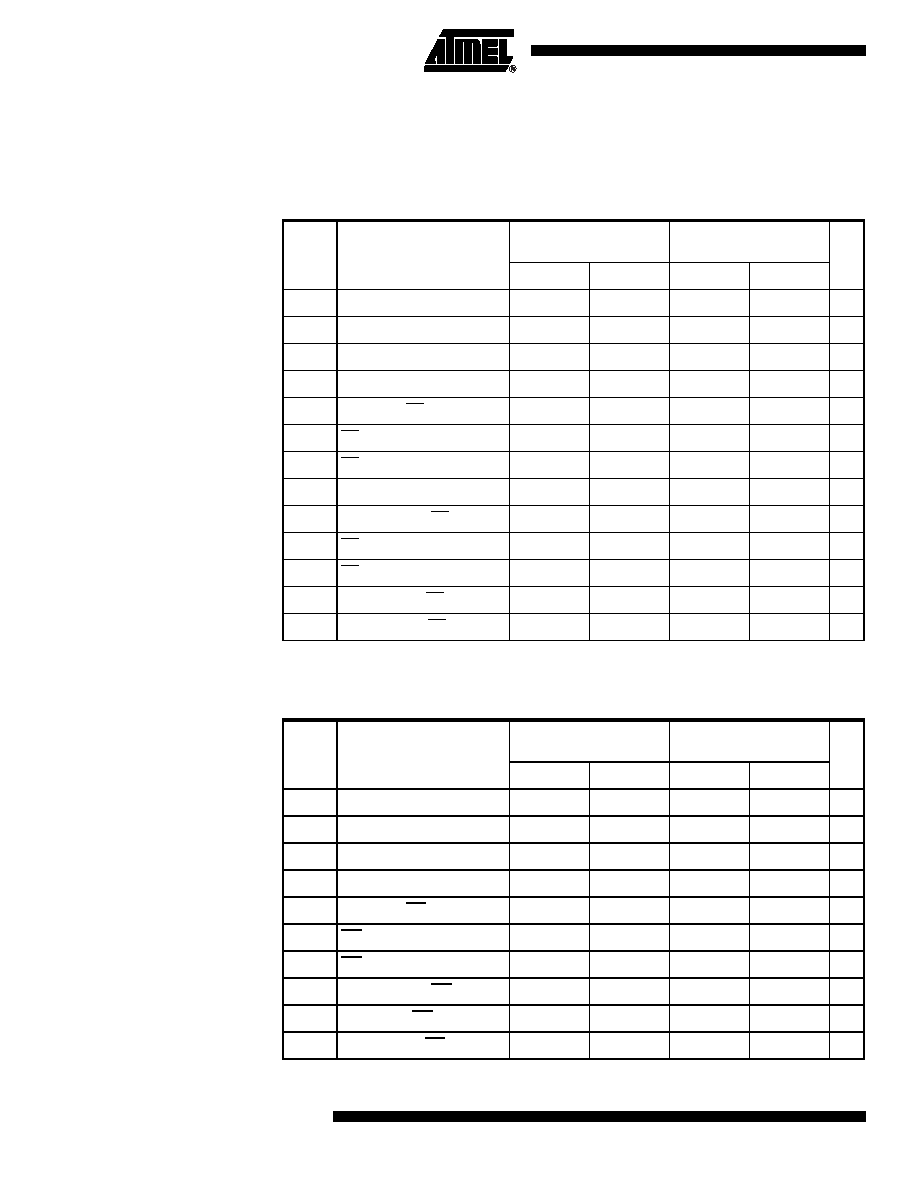

Table 30. External IDE 16-bit Bus Cycle - Data Read AC Timings

VDD = 2.7 to 3.3 V, TA = -40 to +85°C

Table 31. External IDE 16-bit Bus Cycle - Data Write AC Timings

VDD = 2.7 to 3.3 V, TA = -40 to +85°C

Symbol

Parameter

Variable Clock

Standard Mode

Variable Clock

X2 Mode

Unit

Min

Max

Min

Max

TCLCL

Clock Period

50

ns

TLHLL

ALE Pulse Width

2TCLCL-15

TCLCL-15

ns

TAVLL

Address Valid to ALE Low

TCLCL-20

0.5TCLCL-20

ns

TLLAX

Address hold after ALE Low

TCLCL-20

0.5TCLCL-20

ns

TLLRL

ALE Low to RD Low

3TCLCL-30

1.5TCLCL-30

ns

TRLRH

RD Pulse Width

6TCLCL-25

3TCLCL-25

ns

TRHLH

RD high to ALE High

TCLCL-20

TCLCL+20

0.5TCLCL-20 0.5TCLCL+20

ns

TAVDV

Address Valid to Valid Data In

9TCLCL-65

4.5TCLCL-65

ns

TAVRL

Address Valid to RD Low

4TCLCL-30

2TCLCL-30

ns

TRLDV

RD Low to Valid Data

5TCLCL-30

2.5TCLCL-30

ns

TRLAZ

RD Low to Address Float

0

ns

TRHDX

Data Hold After RD High

0

ns

TRHDZ

Data Float After RD High

2TCLCL-25

TCLCL-25

ns

Symbol

Parameter

Variable Clock

Standard Mode

Variable Clock

X2 Mode

Unit

Min

Max

Min

Max

TCLCL

Clock Period

50

ns

TLHLL

ALE Pulse Width

2TCLCL-15

TCLCL-15

ns

TAVLL

Address Valid to ALE Low

TCLCL-20

0.5TCLCL-20

ns

TLLAX

Address hold after ALE Low

TCLCL-20

0.5TCLCL-20

ns

T

LLWL

ALE Low to WR Low

3T

CLCL-30

1.5T

CLCL-30

ns

T

WLWH

WR Pulse Width

6T

CLCL-25

3T

CLCL-25

ns

T

WHLH

WR High to ALE High

T

CLCL-20

T

CLCL+20

0.5T

CLCL-20

0.5T

CLCL+20

ns

T

AVWL

Address Valid to WR Low

4T

CLCL-30

2T

CLCL-30

ns

T

QVWH

Data Valid to WR High

7T

CLCL-20

3.5T

CLCL-20

ns

T

WHQX

Data Hold after WR High

T

CLCL-15

0.5T

CLCL-15

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT89C51SND2C-7FTUL

IC 8051 MCU FLASH 64K MP3 100BGA

AT89C52-24PI

IC MICRO CTRL 24MHZ 40DIP

AT89C55WD-24AU

IC 8051 MCU FLASH 20K 44TQFP

AT89EB5114-TGSIL

IC 8051 MCU FLASH 4K 20SOIC

AT89LP214-20PU

MCU 8051 2K FLASH 20MHZ 14-PDIP

AT89LP216-20SU

MCU 8051 2K FLASH 20MHZ 16-SOIC

AT89LP4052-20SU

IC 8051 MCU FLASH 4K 20SOIC

AT89LP428-20AU

MCU 8051 4K FLASH SPI 32TQFP

相关代理商/技术参数

AT89C51SND1C-DDV

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Single-Chip Flash Microcontroller with MP3 Decoder and Human Interface

AT89C51SND1C-DDW

功能描述:8位微控制器 -MCU Microcontroller

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51SND1CDNC-ROTIL

制造商:Atmel Corporation 功能描述:

AT89C51SND1C-ROTIL

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Single-Chip Flash Microcontroller with MP3 Decoder and Guman Interface

AT89C51SND1C-ROTUL

功能描述:8位微控制器 -MCU MP3 FLASH - VER. 3.3 V COM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51SND2C

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Single-Chip Flash Microcontroller with MP3 Decoder with Full Audio Interface

AT89C51SND2C-7FRIL

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Single-Chip Flash Microcontroller with MP3 Decoder with Full Audio Interface

AT89C51SND2C-7FRJL

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Single-Chip Flash Microcontroller with MP3 Decoder with Full Audio Interface